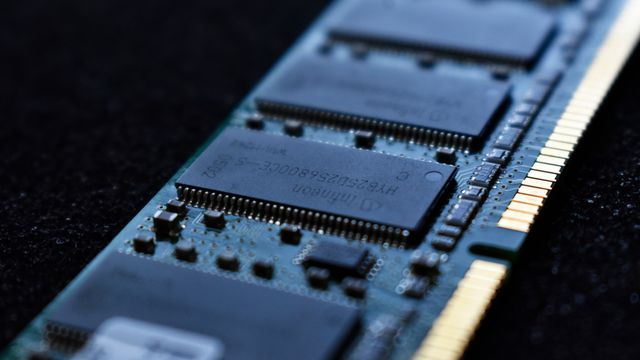

DRAM 3D irá permitir novo salto na densidade das memórias RAM

Por Daniel Trefilio | Editado por Jones Oliveira | 05 de Setembro de 2023 às 10h15

Os chips DRAM com estrutura 3D estão mais próximos de se tornarem realidade, abrindo portas para novos patamares de densidade de memória RAM. Atualmente, por se tratarem de chips 2D, a área das PCBs acaba sendo o maior limitador de até onde é possível expandir o volume de memória por módulo.

Segundo pesquisa recente da Lam Research, criar DRAM 3D não consiste apenas em empilhar silícios, por conta de como os chips 2D são estruturados. No entanto, a empresa especializada em desenvolvimento e pesquisa em semicondutores apresentou um estudo com uma possível solução para a questão.

Mais do que só empilhar

Resumidamente, os chips de DRAM são conjuntos de transistores, capacitores, atravessados por uma trilha elétrica perpendicular, organizados em uma nanofolha de silício. Enquanto a trilha transmite corrente elétrica, os transistores abrem e fecham a comunicação com os capacitores que acumulam essa carga. Isso cria as séries NAND (NOT/AND) binárias de informação, onde os números correspondem a capacitores com carga (1), ou sem carga (0).

Dessa forma, para aumentar a “quantidade de memória”, é necessário estender essas trilhas. Uma analogia fácil é pensar em uma rua: quanto maior a rua, mais casas é possível construir, e mais dados — no caso pessoas — armazenar. A solução prática mais lógica para abrigar mais pessoas é a verticalização das cidades, com os prédios.

No caso das memórias, a principal limitação para simplesmente empilhar esses componentes é a alta densidade que elas teriam em uma área tão menor. No mínimo, isso poderia gerar problemas de interferência e aquecimento, sendo necessário reimaginar a arquitetura da DRAM para viabilizar o empilhamento.

A solução, ainda em desenvolvimento, apresentada pela Lam Research é introduzir transistores na própria estrutura da nanofolha, e transpor a trilha condutora para o lado oposto. Isso permite criar capacitores mais largos, uma vez que os transistores são muito mais estreitos, reduzindo a área ativa de corrente. Dessa forma, a área das PCBs pode ser mais bem aproveitada, representando um salto gigantesco na escalabilidade de memórias.

Por mais que o conceito solucione a maior barreira de escalabilidade de memórias, ele ainda não tem uma data para ser implementado, uma vez que ainda não existem ferramentas eficientes para fabricar essa estrutura. As memórias NAND estão no centro do desenvolvimento de eletrônicos e uma reformulação completa dessa arquitetura tem impacto direto em toda a indústria.